## QSFP28-100G-DCO-A1-C-C

Cisco® Compatible (with select systems) TAA 100GBase-ZR QSFP28 Transceiver (SMF, 1528.77nm to 1567.13nm, 80km, LC, DOM) AutoTune

### Features:

- Hot-Pluggable QSFP28 Form Factor

- IEEE 100G Ethernet (CAUI-4) Compliant Host Interface

- Transmission Reach up to 80km Unamplified (Loss Limited) or up to 120km Amplified (Dispersion Limited, Optionally Extendable to 300km)

- Full C-Band AutoTune, 50GHz/100GHz Spacing

- Operating Temperature: 0 to 70 Celsius

- Power Dissipation: 5.5W

- RoHS Compliant and Lead-Free

- Please contact your sales representative for specific system information

- Please contact your sales representative for specific system information

### Applications:

- 100GBase Ethernet

- Duplex Mux

### Product Description

This Cisco® compatible (with select systems) QSFP28 transceiver provides 100GBase-ZR throughput up to 80km over single-mode fiber (SMF) using a wavelength of 1528.77nm to 1567.13nm, with 100GHz spacing via an LC connector. It can operate at temperatures between 0 and 70C. Our transceiver is built to meet or exceed OEM specifications and is guaranteed to be 100% compatible with Cisco®. It has been programmed, uniquely serialized, and tested for data-traffic and application to ensure that it will initialize and perform identically. All of our transceivers comply with Multi-Source Agreement (MSA) standards to provide seamless network integration. Additional product features include Digital Optical Monitoring (DOM) support which allows access to real-time operating parameters. This transceiver is Trade Agreements Act (TAA) compliant. We stand behind the quality of our products and proudly offer a limited lifetime warranty.

ProLabs' transceivers are RoHS compliant and lead-free.

TAA refers to the Trade Agreements Act (19 U.S.C. & 2501-2581), which is intended to foster fair and open international trade. TAA requires that the U.S. Government may acquire only "U.S.-made or designated country end products."

### Absolute Maximum Ratings

| Parameter                                      | Symbol               | Min. | Typ. | Max. | Unit | Notes |

|------------------------------------------------|----------------------|------|------|------|------|-------|

| DC Supply Voltage                              | Vcc                  | -0.3 |      | 3.6  | V    |       |

| Low-Speed I/O Voltages                         |                      | -0.3 |      | 3.6  | V    |       |

| Storage Temperature                            | Tstg                 | -40  |      | 85   | °C   |       |

| Operating Case Temperature                     | Long-Term            | Tc   | 0    | 70   | °C   | 1     |

|                                                | Short-Term <96 Hours |      | -5   | 75   | °C   |       |

| Operating Relative Humidity                    | RH                   | 5    |      | 95   | %    |       |

| Rx Input Power                                 | PRx,in               |      |      | 10   | dBm  |       |

| ESD Damage Threshold<br>Human Body Model (HBM) | DC Pins              |      | 2000 |      | V    |       |

|                                                | RF Pins              |      | 1000 |      | V    |       |

### Notes:

1. Central office applications.

2. Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the datasheet. Exposure to Absolute Maximum Ratings for extended periods of time can adversely affect device reliability. Use of controls or adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

### Host Interface Modes

| Host Interface ID [18] | Host Interface Description [18] | Modulation | Forward Error Correction Code | Nominal Symbol Rate (GBd) | Supported Line Interface IDs [18] |

|------------------------|---------------------------------|------------|-------------------------------|---------------------------|-----------------------------------|

| 65 [8]                 | CAUI-4 C2M without FEC          | NRZ        | None                          | 25.78125                  | 68, 192, 193                      |

| 66 [8]                 | CAUI-4 C2M with RS(528,514) FEC | NRZ        | RS(528,514)                   | 25.78125                  | 68, 192, 193                      |

## Electrical Characteristics

| Parameter                                                       | Symbol    | Min.    | Typ. | Max.    | Unit | Notes                                           |

|-----------------------------------------------------------------|-----------|---------|------|---------|------|-------------------------------------------------|

| <b>Power Supply – General</b>                                   |           |         |      |         |      |                                                 |

| <b>Power Supply Voltages</b>                                    |           | 3.135   | 3.3  | 3.465   | V    | Including ripple, droop, and noise below 100kHz |

| <b>Host RMS Noise Output</b>                                    |           |         |      | 25      | mV   | 10Hz - 10MHz                                    |

| <b>Module RMS Noise Output</b>                                  |           |         |      | 15      | mV   | 10Hz - 10MHz                                    |

| <b>Module Supply Noise Tolerance</b>                            | PSNRmod   |         |      | 66      | mV   | 10Hz - 10MHz, peak-to-peak                      |

| <b>Module Inrush</b>                                            | Tip       |         |      | 50      | µs   | Instantaneous peak duration                     |

|                                                                 | Tinit     |         |      | 500     | ms   | Initialization time                             |

| <b>Power Supply – Low-Power Mode</b>                            |           |         |      |         |      |                                                 |

| <b>Power Dissipation</b>                                        | Plp       |         |      | 1.5     | W    |                                                 |

| <b>Power Supply Current</b>                                     | Icc,ip,lp |         |      | 600     | mA   | Instantaneous peak current                      |

|                                                                 | Icc,sp,lp |         |      | 495     | mA   | Sustained peak current                          |

|                                                                 | Icc,lp    |         |      | 478     | mA   | 1, Steady state current                         |

| <b>Power Supply – High-Power Mode</b>                           |           |         |      |         |      |                                                 |

| <b>Power Dissipation</b>                                        | Php       |         |      | 5.5     | W    |                                                 |

| <b>Power Supply Current</b>                                     | Icc,ip,hp |         |      | 2200    | mA   | Instantaneous peak current                      |

|                                                                 | Icc,sp,hp |         |      | 1815    | mA   | Sustained peak current                          |

|                                                                 | Icc,hp    |         |      | 1754    | mA   | 1, Steady state current                         |

| <b>Low-Speed I/O</b>                                            |           |         |      |         |      |                                                 |

| <b>Clock Frequency (SCL)</b>                                    | fsCL      |         | 400  |         | kHz  | Default                                         |

|                                                                 |           |         | 1000 |         |      | Fast-mode+                                      |

| <b>Output Voltage (SCL and SDA)</b>                             | VOL       | 0.0     |      | 0.4     |      | Output low                                      |

|                                                                 | VOH       | Vcc-0.5 |      | Vcc+0.3 |      | Output high                                     |

| <b>Input Voltage (SCL and SDA)</b>                              | VIL       | -0.3    |      | 0.3×Vcc | V    | Input low                                       |

|                                                                 | VIH       | 0.7×Vcc |      | Vcc+0.5 |      | Input high                                      |

| <b>Capacitance for SCL and SDA I/O Signal</b>                   | Ci        |         |      | 14      | pF   |                                                 |

| <b>Total Bus Capacitive Load for SCL and SDA</b>                | Cb        |         |      | 100     | pF   | 2, 3.0kΩ pull-up resistor, maximum              |

|                                                                 |           |         |      | 200     |      | 2, 1.6kΩ pull-up resistor, maximum              |

| <b>Input Voltage/Current, LPMode/TxDis, ResetL, and ModSell</b> | VIL       | -0.3    |      | 0.8     | V    | Input voltage, low                              |

|                                                                 | VIH       | 2.0     |      | Vcc+0.3 |      | Input voltage, high                             |

|                                                                 | Iin       | -365    |      | 125     | µA   | Input current, 0V < VIN < Vcc                   |

| <b>Output Voltage, ModPrsL, and IntL/RxLOSL</b>                 | VOL       | 0.0     |      | 0.4     | V    | Output low, IOL = 2mA                           |

|                                                                 | VOH       | Vcc-0.5 |      | Vcc+0.3 |      | Output high, 10kΩ pull-up resistor to Host_Vcc  |

### Notes:

1. The module will stay within its advertised power class for all supply voltages.

2. For 1000kHz clock rate.

## Optical Characteristics

| Parameter                                                      | Symbol           | Min.     | Typ.  | Max.  | Unit     | Notes                                                                 |

|----------------------------------------------------------------|------------------|----------|-------|-------|----------|-----------------------------------------------------------------------|

| <b>Power Supply – General</b>                                  |                  |          |       |       |          |                                                                       |

| <b>Symbol Rate</b>                                             | Rbaud            |          | 27.95 |       | GBd      |                                                                       |

| <b>Modulation Format</b>                                       |                  | DP-DQPSK |       |       |          |                                                                       |

| <b>Channel Frequency Range</b>                                 | Vc               | 191.4    | 193.7 | 196.1 | THz      | 100GHz grid                                                           |

|                                                                | Vc               | 191.35   | 193.7 | 196.1 | THz      | 50GHz grid                                                            |

| <b>Channel Spacing</b>                                         | $\Delta Vc$      |          | 100   |       | GHz      | 100GHz grid                                                           |

|                                                                | $\Delta Vc$      |          | 50    |       | GHz      | 50GHz grid                                                            |

| <b>Frequency Accuracy</b>                                      | $\delta Vc$      | -1.8     |       | 1.8   | GHz      |                                                                       |

| <b>Laser Intrinsic Linewidth</b>                               | LW               |          |       | 500   | kHz      | Calculated based on FM noise Power Spectral Density (PSD) measurement |

| <b>Side-Mode Suppression Ratio</b>                             | SMSR             | 40       |       |       | dB       | No modulation                                                         |

| <b>Relative Intensity Noise</b>                                | RIN              |          |       | -140  | dB/Hz    | Peak over 0.2GHz < f < 10GHz                                          |

| <b>Transmitter</b>                                             |                  |          |       |       |          |                                                                       |

| <b>Tx Output Power</b>                                         | PTx,out          | -8       |       | -4    | dBm      |                                                                       |

| <b>Tx Output Power Monitor Range</b>                           | PTx,mon          | -10      |       | -2    | dBm      |                                                                       |

| <b>Tx Output Power Monitor Accuracy</b>                        | $\delta PTx,mon$ | -1.5     |       | 1.5   | dB       | Tx optical power monitor reading relative to actual Tx output power   |

| <b>Tx Output Power During Tuning or When Tx is Disabled</b>    | PTx,dark         |          |       | -35   | dBm      |                                                                       |

| <b>Tx Spectral Excursion</b>                                   |                  | -15      |       | 15    | GHz      | ITU-T G.698.2 §7.2.3 [11]                                             |

| <b>Tx Output Power Imbalance Between X and Y Polarizations</b> | $\Delta P_{X/Y}$ |          |       | 1.5   | dB       |                                                                       |

| <b>Tx XY Skew</b>                                              |                  |          |       | 6.0   | ps       |                                                                       |

| <b>Tx IQ Offset</b>                                            |                  |          |       | -25   | dB       |                                                                       |

| <b>Tx IQ Imbalance</b>                                         |                  |          |       | 1.0   | dB       |                                                                       |

| <b>Tx Quadrature Error</b>                                     |                  | -7.0     |       | 7.0   | °        |                                                                       |

| <b>Tx IQ Skew</b>                                              |                  |          |       | 1.5   | ps       |                                                                       |

| <b>Tx Error Vector Magnitude Mask Ratio</b>                    |                  |          |       | 23    | %        | ITU-T G.698.2 §7.2.12 [11], with 24dB/0.1nm noise loading             |

| <b>Tx In-Band Optical Signal to Noise Ratio</b>                | OSNRin           | 40       |       |       | dB/0.1nm | Under modulation, $ \Delta f  < 60\text{GHz}$                         |

| <b>Tx Out-of-Band Optical Signal to Noise Ratio</b>            | OSNRout          | 35       |       |       | dB/0.1nm | Under modulation, $ \Delta f  > 60\text{GHz}$ , excl. side-mode peaks |

| <b>Tx Reflectance</b>                                          |                  |          |       | -20   | dB       |                                                                       |

| <b>Receiver</b>                                                |                  |          |       |       |          |                                                                       |

| <b>Rx Total Input Power</b>                                    | PRx,tot          | -30      |       | 3     | dBm      | Broadband                                                             |

| <b>Rx Signal Input Power (Amplified)</b>                       | PRx,sig          | -18      |       | 1     | dBm      | Full Rx OSNR tolerance                                                |

|                                                                |                  | -22      |       | 3     | dBm      | 1                                                                     |

|                                                       |                      |                     |      |     |          |                                                     |                                  |  |

|-------------------------------------------------------|----------------------|---------------------|------|-----|----------|-----------------------------------------------------|----------------------------------|--|

| <b>Rx OSNR Tolerance</b>                              | <b>100G DQPSK SC</b> |                     | 16.5 |     |          | dB/0.1nm                                            | Back-to-back, $PRx,sig > -18dBm$ |  |

|                                                       | <b>100G DQPSK RS</b> |                     | 21.5 |     |          |                                                     |                                  |  |

| <b>CD Tolerance</b>                                   |                      |                     |      | 2.4 | ns/nm    | OSNR penalty < 0.5dB                                |                                  |  |

| <b>PMD Tolerance</b>                                  |                      |                     |      | 10  | Ps       |                                                     |                                  |  |

| <b>DGD Tolerance</b>                                  |                      |                     |      | 20  | Ps       |                                                     |                                  |  |

| <b>Tolerance to Change in SOP</b>                     |                      |                     |      | 50  | krad/s   |                                                     |                                  |  |

| <b>PDL OSNR Penalty</b>                               | <b>1dB PDL</b>       |                     |      | 0.5 | dB/0.1nm | Change in principal state of polarization < 1rad/ms |                                  |  |

|                                                       | <b>2dB PDL</b>       |                     |      | 1.0 |          |                                                     |                                  |  |

|                                                       | <b>4dB PDL</b>       |                     |      | 3.0 |          |                                                     |                                  |  |

| <b>Rx Signal Input Power Transient Amplitude</b>      |                      | -3                  |      | 3   | dB       | 2                                                   |                                  |  |

| <b>Rx Signal Input Power Transient Rise/Fall Time</b> |                      | 100                 |      |     | μs       | 3                                                   |                                  |  |

| <b>Rx Signal Input Power (Unamplified)</b>            | <b>100G DQPSK SC</b> | -30                 |      | 1   | dBm      | OSNR > 35dB/0.1nm                                   |                                  |  |

|                                                       | <b>100G DQPSK RS</b> | -24                 |      | 1   |          |                                                     |                                  |  |

| <b>Rx Signal Input Power Monitor Range</b>            |                      | $PRx,mon(s)$        | -21  |     | dBm      |                                                     |                                  |  |

| <b>Rx Signal Input Power Monitor Accuracy</b>         |                      | $\delta PRx,mon(s)$ | -2.5 |     | dB       |                                                     |                                  |  |

| <b>Rx Total Input Power Monitor Range</b>             |                      | $PRx,mon(t)$        | -21  |     | dBm      |                                                     |                                  |  |

| <b>Rx Total Input Power Monitor Accuracy</b>          |                      | $\delta PRx,mon(t)$ | -2.0 |     | dB       |                                                     |                                  |  |

| <b>Rx Reflectance</b>                                 |                      |                     |      | -20 | dB       |                                                     |                                  |  |

**Notes:**

1. Extended range. Rx signal input power range over which performance can be guaranteed with <1dB OSNR penalty relative to the Rx OSNR tolerance limit.

2. Peak excursion from steady state, transient within Rx signal input power (amplified) range, and OSNR penalty <0.5dB.

3. Rise/fall time for the above peak excursion, OSNR penalty <0.5dB.

## SFF-8636 Management Interface

| Parameter                                   | Symbol | Min. | Max. | Unit | Conditions                                                                                                                                                      | Notes |

|---------------------------------------------|--------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <b>Initialization Time</b>                  |        |      | 120  | s    | Time from power on or hot plug until the module is fully functional (assuming LPMode pulled low by the host).                                                   | 2, 3  |

| <b>Reset Init Assert Time</b>               |        | 10   |      | μs   | Minimum pulse time on the ResetL signal to initiate a module reset.                                                                                             |       |

| <b>Serial Bus Hardware Ready Time</b>       |        |      | 2    | s    | Time from power on until the module responds to data transmission over the 2-wire serial bus.                                                                   | 2     |

| <b>Monitor Data Ready Time</b>              |        |      | 2    | s    | Time from power on to Data_Not_Ready, Byte 2 bit 0, cleared to 0, and IntL output pulled low.                                                                   | 2     |

| <b>Reset Assert Time</b>                    |        |      | 120  | s    | Time from a rising edge on the ResetL input until the module is fully functional.                                                                               | 3     |

| <b>LPMode/TxDis Mode Change Time</b>        |        |      | 100  | ms   | Time to change between LPMode and TxDis modes of the dual-mode signal LPMode/TxDis.                                                                             |       |

| <b>LPMode Assert Time</b>                   |        |      | 100  | ms   | Time from when the host releases LPMode to high until module power consumption reaches Power Class 1.                                                           |       |

| <b>LPMode De-Assert Time</b>                |        |      | 120  | s    | Time from when the host pulls LPMode low until the module is fully functional.                                                                                  | 3     |

| <b>IntL/RxLOSL Mode Change Time</b>         |        |      | 100  | ms   | Time to change between IntL and RxLOSL modes of the dual-mode signal IntL/RxLOSL.                                                                               |       |

| <b>IntL Assert Time</b>                     |        |      | 200  | ms   | Time from occurrence of condition triggering an interrupt until IntL is low.                                                                                    |       |

| <b>IntL De-Assert Time</b>                  |        |      | 500  | μs   | Time from clear on read operation of associated flag until module releases IntL to high. This includes the time to clear Rx LOS, Tx Fault, and other flag bits. | 4     |

| <b>RxLOSL Assert Time</b>                   |        |      | 1    | ms   | Time from optical loss of signal to RxLOSL signal pulled low by the module.                                                                                     |       |

| <b>RxLOSL De-Assert Time</b>                |        |      | 3    | ms   | Time from optical signal above the LOS de-assert threshold to when the module releases the RxLOSL signal to high.                                               |       |

| <b>Tx Fault Assert Time</b>                 |        |      | 200  | ms   | Time from Tx Fault state to Tx Fault bit set to 1 and IntL pulled low by the module.                                                                            |       |

| <b>Flag Assert Time</b>                     |        |      | 200  | ms   | Time from condition triggering flag to associated flag bit set to 1 and IntL pulled low by the module.                                                          |       |

| <b>Mask Assert Time</b>                     |        |      | 100  | ms   | Time from mask bit set to 1 until the module is prevented from pulling IntL low when the associated flag is set high.                                           | 1     |

| <b>Mask De-Assert Time</b>                  |        |      | 100  | ms   | Time from mask bit cleared to 0 until module is enabled to pull IntL low when the associated flag is set high.                                                  | 1     |

| <b>I/O Timing for Squelch &amp; Disable</b> |        |      |      |      |                                                                                                                                                                 |       |

| <b>Rx Squelch Assert Time</b>               |        |      | 15   | ms   | Time from loss of Rx input signal until the squelched output condition is reached.                                                                              |       |

| <b>Rx Squelch De-Assert Time</b>            |        |      | 15   | ms   | Time from resumption of Rx input signals until normal Rx output condition is reached.                                                                           |       |

| <b>Tx Squelch Assert Time</b>               |        |      | 400  | ms   | Time from loss of Tx input signal until the squelched output condition is reached.                                                                              |       |

| <b>Tx Squelch De-Assert Time</b>            |        |      | 10   | s    | Time from resumption of Tx input signal until the normal Tx output condition is reached.                                                                        |       |

| <b>Tx Disable Assert Time</b>               |        |      | 1    | ms   | Time from Tx_Disable bit is set to 1 until optical output falls below 10% of nominal.                                                                           | 1     |

| <b>Tx Disable De-Assert Time</b>            |        |      | 10   | s    | Time from Tx Disable bit cleared to 0 until optical output rises above 90% of nominal.                                                                          | 1     |

|                                         |  |  |     |    |                                                                                                                         |   |

|-----------------------------------------|--|--|-----|----|-------------------------------------------------------------------------------------------------------------------------|---|

| <b>Rx Output Disable Assert Time</b>    |  |  | 100 | ms | Time from Rx Output Disable bit set (value= 1b) until Rx output falls below 10% of nominal.                             | 1 |

| <b>Rx Output Disable De-Assert Time</b> |  |  | 100 | ms | Time from Rx Output Disable bit cleared (value= 0b) until Rx output rises above 90% of nominal.                         | 1 |

| <b>Squelch Disable Assert Time</b>      |  |  | 100 | ms | This applies to Rx and Tx Squelch and is the time from bit set (value = 1b) until squelch functionality is disabled.    | 1 |

| <b>Squelch Disable De-Assert Time</b>   |  |  | 100 | ms | This applies to Rx and Tx Squelch and is the time from bit cleared (value = 0b) until squelch functionality is enabled. | 1 |

**Notes:**

1. Measured from the rising edge of SDA during STOP sequence of write transaction.

2. “Power On” is defined as the instant when supply voltages reach and remain at or above the minimum level specified.

3. “Fully Functional” is defined as the module being ready to transmit and receive valid signals and all management interface data, including monitors, being valid. It is indicated after “Reset” or “Hot Plug” by the module releasing IntL to “high” after the host has read a 0 from the Data\_Not\_Ready flag bit. Rx LOS condition is defined as (a) Rx input power below threshold or (b) DSP loss of signal.

4. Measured from rising edge of the SDA during STOP sequence of read transaction.

**Optical Timing Characteristics**

| Parameter                        | Symbol | Min. | Max. | Unit | Conditions | Notes |

|----------------------------------|--------|------|------|------|------------|-------|

| <b>Tx Turn On Time</b>           |        |      | 10   | s    | Warm Start | 1     |

|                                  |        |      | 120  | s    | Cold Start |       |

| <b>Rx Acquisition Time</b>       |        |      | 30   | ms   | Warm Start |       |

|                                  |        |      | 120  | s    | Cold Start |       |

| <b>Tx/Rx Channel Tuning Time</b> |        |      | 30   | s    |            |       |

**Notes:**

1. Assumes the Tx/Rx laser is already tuned to the correct frequency.

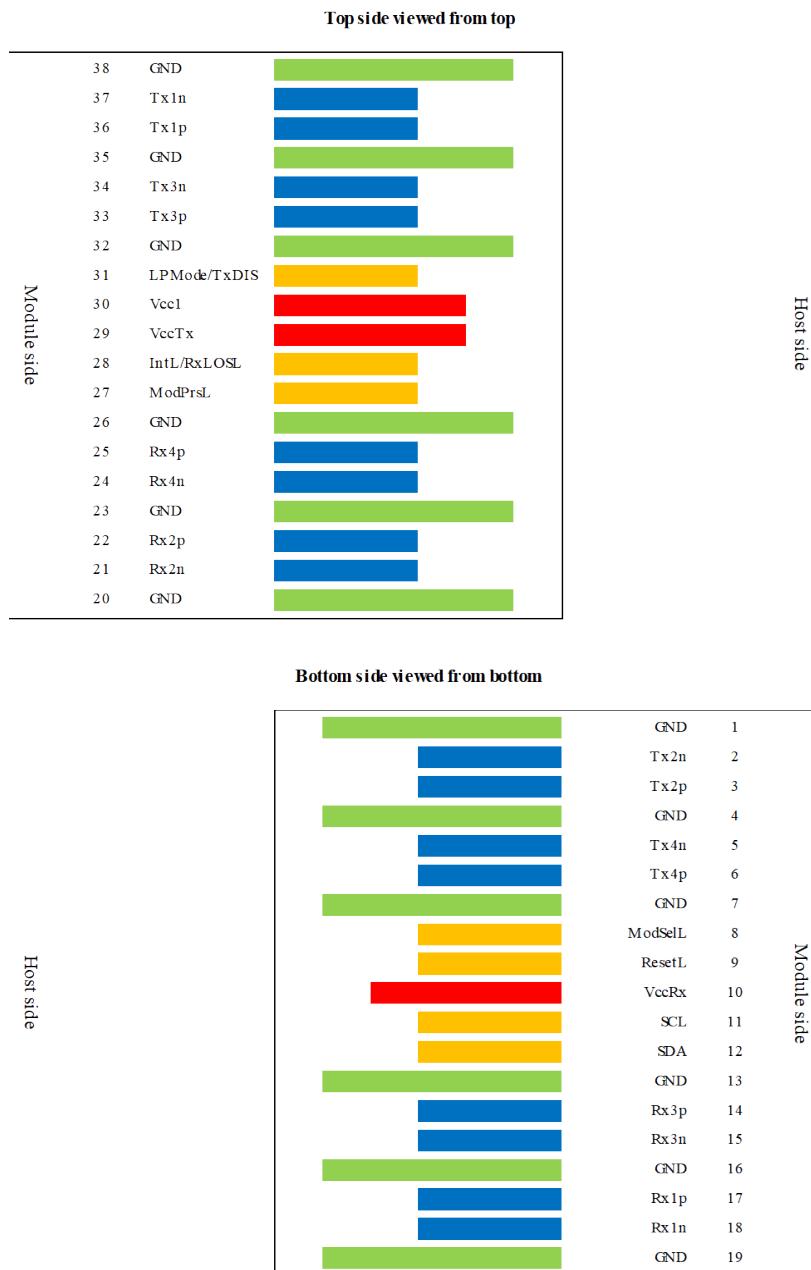

## Pin Descriptions

| Pin | Logic      | Symbol       | Name/Description                                                                          | Plug Sequence | Notes |

|-----|------------|--------------|-------------------------------------------------------------------------------------------|---------------|-------|

| 1   |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 2   | CML-I      | Tx2-         | Transmitter Inverted Data Input.                                                          | 3             |       |

| 3   | CML-I      | Tx2+         | Transmitter Non-Inverted Data Input.                                                      | 3             |       |

| 4   |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 5   | CML-I      | Tx4-         | Transmitter Inverted Data Input.                                                          | 3             |       |

| 6   | CML-I      | Tx4+         | Transmitter Non-Inverted Data Input.                                                      | 3             |       |

| 7   |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 8   | LVTTI-I    | ModSelL      | Module Select.                                                                            | 3             |       |

| 9   | LVTTI-I    | ResetL       | Module Reset.                                                                             | 3             |       |

| 10  |            | VccRx        | +3.3V Receiver Power Supply.                                                              | 2             | 2     |

| 11  | LVCMOS-I/O | SCL          | 2-Wire Serial Interface Clock.                                                            | 3             |       |

| 12  | LVCMOS-I/O | SDA          | 2-Wire Serial Interface Data.                                                             | 3             |       |

| 13  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 14  | CML-O      | Rx3+         | Receiver Non-Inverted Data Output.                                                        | 3             |       |

| 15  | CML-O      | Rx3-         | Receiver Inverted Data Output.                                                            | 3             |       |

| 16  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 17  | CML-O      | Rx1+         | Receiver Non-Inverted Data Output.                                                        | 3             |       |

| 18  | CML-O      | Rx1-         | Receiver Inverted Data Output.                                                            | 3             |       |

| 19  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 20  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 21  | CML-O      | Rx2-         | Receiver Inverted Data Output.                                                            | 3             |       |

| 22  | CML-O      | Rx2+         | Receiver Non-Inverted Data Output.                                                        | 3             |       |

| 23  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 24  | CML-O      | Rx4-         | Receiver Inverted Data Output.                                                            | 3             |       |

| 25  | CML-O      | Rx4+         | Receiver Non-Inverted Data Output.                                                        | 3             |       |

| 26  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 27  | LVTTI-O    | ModPrsL      | Module Present.                                                                           | 3             |       |

| 28  | LVTTI-O    | IntL/RxLOSL  | Interrupt. Optionally configurable as RxLOSL via the management interface (SFF-8636).     | 3             |       |

| 29  |            | VccTx        | +3.3V Transmitter Power Supply.                                                           | 2             | 2     |

| 30  |            | Vcc1         | +3.3V Power Supply.                                                                       | 2             | 2     |

| 31  | LVTTI-I    | LPMode/TxDis | Low-Power Mode. Optionally configurable as TxDis via the management interface (SFF-8636). | 3             |       |

| 32  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 33  | CML-I      | Tx3+         | Transmitter Non-Inverted Data Input.                                                      | 3             |       |

| 34  | CML-I      | Tx3-         | Transmitter Inverted Data Input.                                                          | 3             |       |

| 35  |            | GND          | Module Ground.                                                                            | 1             | 1     |

| 36  | CML-I      | Tx1+         | Transmitter Non-Inverted Data Input.                                                      | 3             |       |

| 37  | CML-I      | Tx1-         | Transmitter Inverted Data Input.                                                          | 3             |       |

| 38  |            | GND          | Module Ground.                                                                            | 1             | 1     |

## Notes:

1. GND is the symbol for signal and supply (power) common for the module. All are common within the module, and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal common ground plane.

2. VccRx, Vcc1, and VccTx are applied concurrently and may be internally connected within the module in any combination.

3. Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1, 2, and 3. See figure below for pad locations.

## Electrical Pad Layout

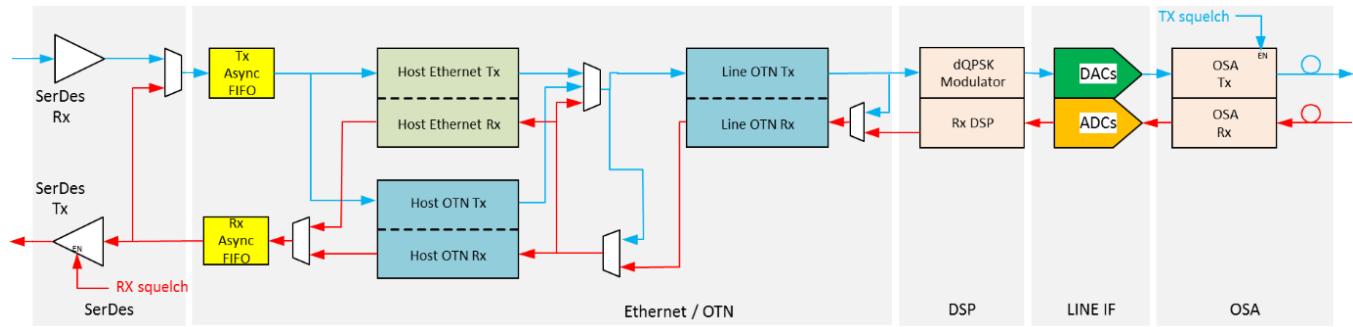

## Block Diagram

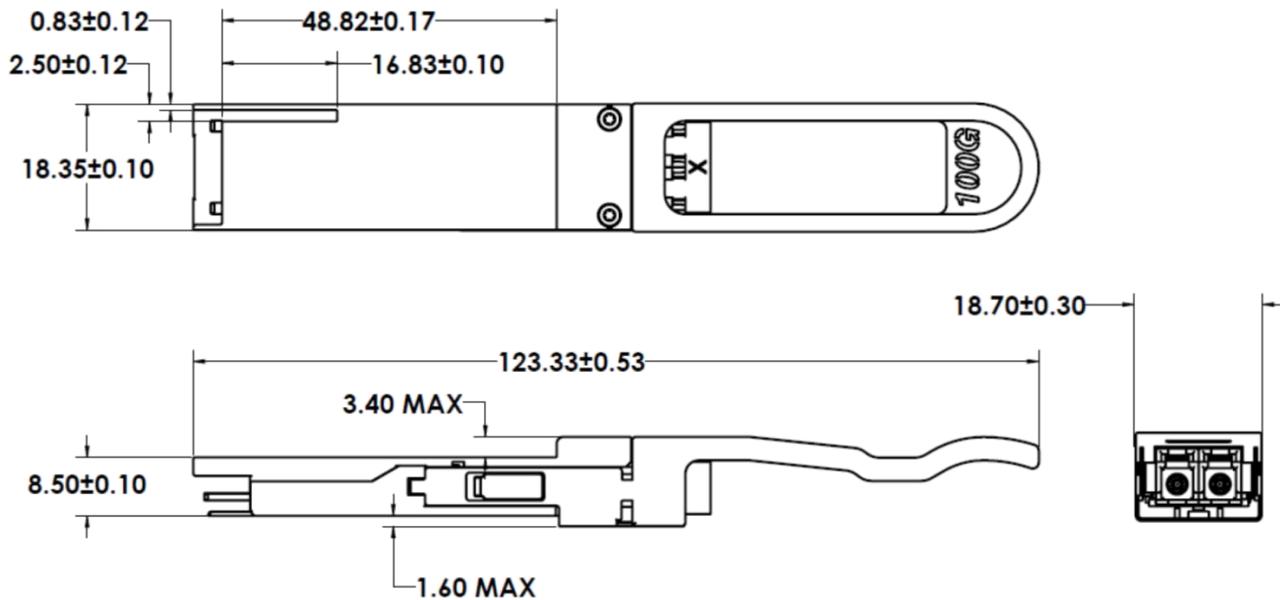

## Mechanical Specifications

## About ProLabs

Our experience comes as standard; for over 15 years ProLabs has delivered optical connectivity solutions that give our customers freedom and choice through our ability to provide seamless interoperability. At the heart of our company is the ability to provide state-of-the-art optical transport and connectivity solutions that are compatible with over 90 optical switching and transport platforms.

## Complete Portfolio of Network Solutions

ProLabs is focused on innovations in optical transport and connectivity. The combination of our knowledge of optics and networking equipment enables ProLabs to be your single source for optical transport and connectivity solutions from 100Mb to 400G while providing innovative solutions that increase network efficiency. We provide the optical connectivity expertise that is compatible with and enhances your switching and transport equipment.

## Trusted Partner

Customer service is our number one value. ProLabs has invested in people, labs and manufacturing capacity to ensure that you get immediate answers to your questions and compatible product when needed. With Engineering and Manufacturing offices in the U.K. and U.S. augmented by field offices throughout the U.S., U.K. and Asia, ProLabs is able to be our customers best advocate 24 hours a day.

## Contact Information

### ProLabs US

Email: [sales@prolabs.com](mailto:sales@prolabs.com)

Telephone: 952-852-0252

### ProLabs UK

Email: [salesupport@prolabs.com](mailto:salesupport@prolabs.com)

Telephone: +44 1285 719 600